# **Precision Operational Amplifier**

# **FEATURES**

Low Offset Voltage: 25µV max

■ Low Drift: 0.3µV/°C

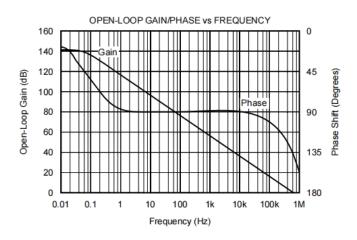

High Open-Loop Gain: 130dB min

Low Quiescent Current: 1.5mA typ

• Replaces Industry-Standard Opamps: OP07, OP77, OPA177,

AD707, ETC

### **ORDERING INFORMATION**

| DEVICE      | Package Type | MARKING | Packing | Packing Qty  |

|-------------|--------------|---------|---------|--------------|

| OP177FN     | DIP-8        | OP177F  | TUBE    | 2000pcs/box  |

| OP177FM/TR  | SOP-8        | OP177F  | REEL    | 2500pcs/reel |

| OP177FMM/TR | MSOP-8       | OP177F  | REEL    | 3000pcs/reel |

| OP177GN     | DIP-8        | OP177G  | TUBE    | 2000pcs/box  |

| OP177GM/TR  | SOP-8        | OP177G  | REEL    | 2500pcs/reel |

| OP177GMM/TR | MSOP-8       | OP177G  | REEL    | 3000pcs/reel |

### **DESCRIPTION**

The OP177 precision bipolar op amp feature very low offset voltage and drift. Laser-trimmed offset, drift and input bias current virtually eliminate the need for costly external trimming. The high performance and low cost make them ideally suited to a wide range of precision instrumentation.

The low quiescent current of the OP177 dramatically reduce warm-up drift and errors due to thermoelectric effects in input interconnections. It provides an effective alternative to chopper-stabilized amplifiers. The low noise of the OP177 maintains accuracy. OP177 performance gradeouts are available. Packaging options include 8-pin plastic DIP and SOP-8 surface-mount packages.

### **APPLICATIONS**

- Precision Instrumentation

- Data Acquisition

- Test Equipment

- Bridge Amplifier

- Thermocouple Amplifier

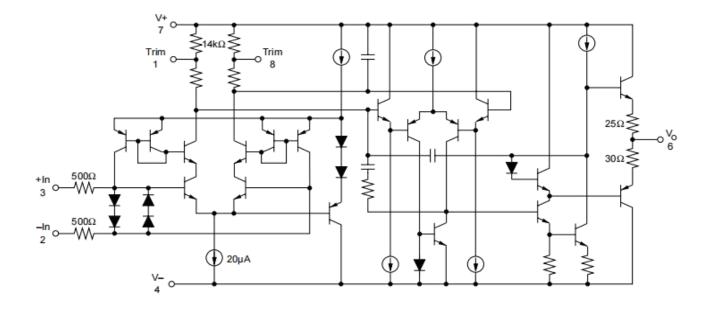

### **BLOCK DIAGRAM**

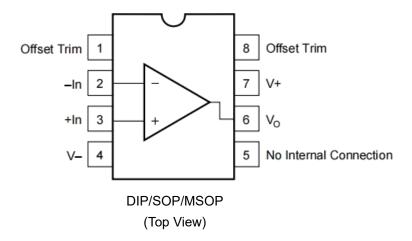

### PIN CONFIGURATION

### **ABSOLUTE MAXIMUM RATINGS**

|                            | Condition          | Min        | Max     |  |  |

|----------------------------|--------------------|------------|---------|--|--|

| Power Supply Voltage       |                    | -22V       | +22V    |  |  |

| Differential Input Voltage |                    | -30V       | +30V    |  |  |

| Input Voltage              |                    | -VS        | +VS     |  |  |

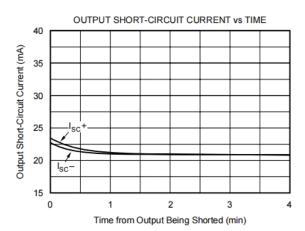

| Output Short Circuit       |                    | Continuous |         |  |  |

|                            | Plastic DIP8, SOP8 | -40°C      | +85°C   |  |  |

| Operating Temperature      | $\theta_{JA}(DIP)$ | -          | 100°C/W |  |  |

|                            | $\theta_{JA}SOP$   | -          | 160°C/W |  |  |

| Storage Temperature        | Plastic DIP8, SOP8 | -65°C      | +125°C  |  |  |

| Junction Temperature       |                    | -          | +150°C  |  |  |

| (soldering, 3s) N package  |                    | -          | +260°C  |  |  |

| Lead Temperature (Solder   | ring, 10 seconds)  | -          | 245°C   |  |  |

**Note**: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is intended to be functional, but specific performance is not ensured.

# **ELECTROSTATIC DISCHARGE SENSITIVITY**

Any integrated circuit can be damaged by ESD. that all integrated circuits be handled with appropriate precautions. ESD can cause damage ranging from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications. ESD test method consists of five 1000V positive and negative discharges (100pF in series with  $1.5k\Omega$ ) applied to each pin. Failure to observe proper handling procedures could result in small changes to the OP177's input bias current.

# **OP177 SPECIFICATIONS**

At  $V_S$  = ±15V,  $T_A$  = +25°C, unless otherwise noted.

|                                        |                                     |       | OP177F |     |      | OP177G | i   |       |

|----------------------------------------|-------------------------------------|-------|--------|-----|------|--------|-----|-------|

| PARAMETER                              | CONDITION                           | MIN   | TYP    | MAX | MIN  | TYP    | MAX | UNITS |

| OFFSET VOLTAGE                         |                                     |       |        |     |      |        |     |       |

| Input Offset Voltage                   |                                     |       | 10     | 25  |      | 20     | 60  | μV    |

| Long-Term Input Offset <sup>(1)</sup>  |                                     |       | 0.3    |     |      | 0.4    |     | μV/Mo |

| Voltage Stability                      |                                     |       |        |     |      |        |     |       |

| Offset Adjustment Range                | $R_P = 20k\Omega$                   |       | ±3     |     |      | *      |     | mV    |

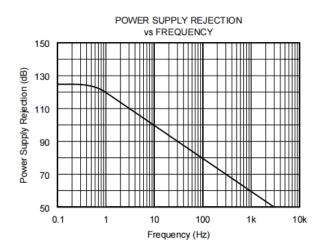

| Power Supply Rejection Ratio           | $Vs = \pm 3V \text{ to} \pm 18V$    | 115   | 125    |     | 110  | 120    |     | dB    |

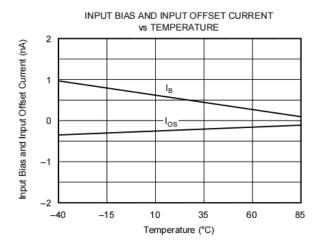

| INPUT BIAS CURRENT                     |                                     |       |        |     |      |        |     |       |

| Input Offset CurrentInput Bias         |                                     |       | 0.3    | 1.5 |      | *      | 2.8 | nA    |

| Current                                |                                     |       | 0.5    | ±2  |      | *      | 2.8 | nA    |

| NOISE                                  |                                     |       |        |     |      |        |     |       |

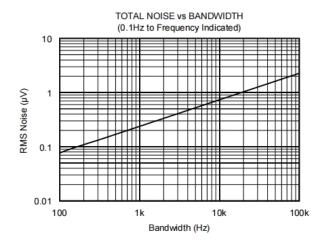

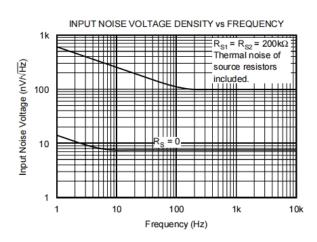

| Input Noise Voltage                    | 1Hz to 100Hz <sup>(2)</sup>         |       | 85     | 150 |      | *      |     | nVrms |

| Input NoiseCurrent                     | 1Hz to 100Hz                        |       | 4.5    |     |      | *      | *   | pArms |

| INPUT IMPEDANCE                        |                                     |       |        |     |      |        |     |       |

| Input Resistance                       | Differential Mode <sup>(3)</sup>    | 26    | 45     |     | 18.5 | *      |     | МΩ    |

|                                        | Common-Mode                         |       | 200    |     |      | *      |     | GΩ    |

| INPUT VOLTAGE RANGE                    |                                     |       |        |     |      |        |     |       |

| Common-Mode Input Range <sup>(4)</sup> |                                     | ±13   | ±14    |     | *    | *      |     | V     |

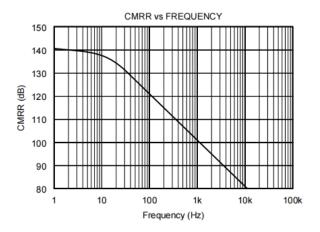

| Common-Mode Rejection                  | $V_{CM} = \pm 13V$                  | 130   | 140    |     | 115  | *      |     | dB    |

| OPEN-LOOP GAIN                         | RL≥2KΩ                              |       |        |     |      |        |     |       |

| Large Signal Voltage Gain              | $V_0 = \pm 10 V^{(5)}$              | 5110  | 12,000 |     | 200  | 6000   |     | V/mV  |

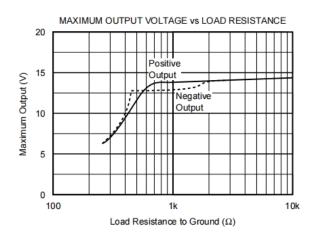

| OUTPUT                                 |                                     |       |        |     |      |        |     |       |

| Output Voltage Swing                   | RL≥10kΩ                             | ±13.5 | ±14    |     | *    | *      |     | V     |

|                                        | RL≥2kΩ                              | ±12.5 | ±13    |     | *    | *      |     | V     |

|                                        | RL≥1kΩ                              | ±12   | ±12.5  |     | *    | *      |     | V     |

| Open-Loop Output Resistance            |                                     |       | 60     |     |      | *      |     | Ω     |

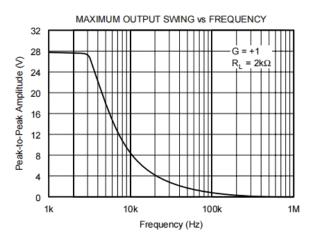

| FREQUENCY RESPONSE                     |                                     |       |        |     |      |        |     |       |

| Slew Rate                              | RL≥2kΩ                              | 0.1   | 0.3    |     | *    | *      |     | V/µs  |

| Closed-Loop Bandwidth                  | G=+1                                | 0.4   | 0.6    |     | *    | *      |     | MHz   |

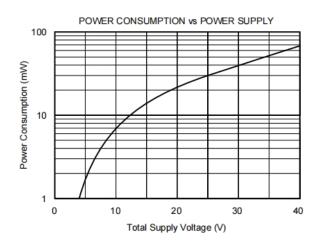

| POWER SUPPLY                           |                                     |       |        |     |      |        |     |       |

| Power Consumption                      | $V_{\text{S}}$ = $\pm$ 15V, No Load |       | 40     | 60  |      | *      | *   | mW    |

|                                        | $V_S = \pm 3V$ , No Load            |       | 3.5    | 4.5 |      | *      | *   | mW    |

| Supply Current                         | $V_S$ =±15V, No Load                |       | 1.3    | 2   |      | *      | *   | mW    |

At  $V_S = \pm 15V$ ,  $-40^{\circ}C \le TA \le +85^{\circ}C$ , unless otherwise noted.

| OFFSET VOLTAGE               |                                   |      |            |     |      |      |     |       |

|------------------------------|-----------------------------------|------|------------|-----|------|------|-----|-------|

| Input Offset Voltage         |                                   |      | 15         | 40  |      | 20   | 100 | μV    |

| Average Input Offset Voltage |                                   |      | 0.1        | 0.3 |      | 0.7  | 1.2 | μν/°C |

| Drift                        |                                   |      | 0.1        | 0.5 |      | 0.7  | 1.2 | μν/ Ο |

| Power Supply Rejection Ratio | $V_S = \pm 3 \text{ to } \pm 18V$ | 110  | 120        |     | 106  | 115  |     | dB    |

| INPUT BIAS CURRENT           |                                   |      |            |     |      |      |     |       |

| Input Offset Current         |                                   |      | 0.5        | 2.2 |      | *    | 4.5 | nA    |

| Average Input Offset Current |                                   |      | 1.5        | 40  |      | *    | 85  | Pa/°C |

| Drift <sup>(6)</sup>         |                                   |      | 1.5        | 40  |      | ~    | 65  | ra, C |

| Input Bias Current           |                                   |      | 0.5        | ±4  |      | *    | ±6  | nA    |

| Average Input Bias Current   |                                   |      | 8          | 40  |      | 15   | 60  | Pa/°C |

| Drift <sup>(6)</sup>         |                                   |      | 0          | 40  |      | 13   | 00  | ra, C |

| INPUT VOLTAGE RANGE          |                                   |      |            |     |      |      |     |       |

| Common-Mode Input Range      |                                   | ±13  | $\pm$ 13.5 |     | *    | *    |     | V     |

| Common-Mode Rejection        | $V_{CM} = \pm 13V$                | 120  | 140        |     | 110  | *    |     | dB    |

| OPEN-LOOP GAIN               |                                   |      |            |     |      |      |     |       |

| Large Signal Voltage Gain    | RL≥2KΩ,V <sub>O</sub> =±10V       | 2000 | 6000       |     | 1000 | 4000 |     | V/mV  |

| OUTPUT                       |                                   |      |            |     |      |      |     |       |

| Output Voltage Swing         | RL≥2KΩ                            | ±12  | ±13        |     | *    | *    |     | V     |

| POWER SUPPLY                 |                                   |      |            |     |      |      |     |       |

| Power Consumption            | $V_S$ = $\pm 15 V$ , No Load      |      | 60         | 75  |      | *    | *   | mW    |

| Supply Current               | $V_S$ = $\pm 15V$ , No Load       |      | 2          | 25  |      | *    | *   | mA    |

<sup>\*</sup>Same as specification for product to left.

#### NOTES

- (2) Sample tested.

- (3) Guaranteed by design.

- (4) Guaranteed by CMRR test condition.

- (5) To insure high open-loop gain throughout the  $\pm 10V$  output range, AOL is tested at  $-10V \le VO \le 0V$ ,  $0V \le VO \le +10V$ , and  $-10V \le VO \le +10V$ .

- (6) Guaranteed by end-point limits.

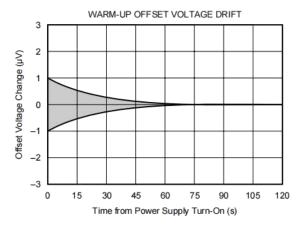

<sup>(1)</sup> Long-Term Input Offset Voltage Stability refers to the averaged trend line of VOS vs time over extended periods after the first 30 days of operation. Excluding the initial hour of operation, changes in VOS during the first 30 operating days are typically less than  $2\mu V$ .

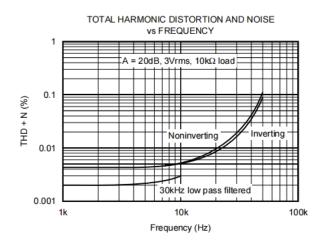

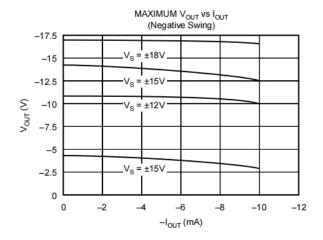

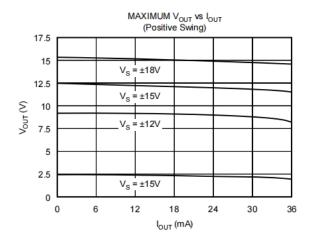

### **TYPICAL PERFORMANCE CURVES**

At  $T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

# **TYPICAL PERFORMANCE CURVES(CONT)**

At  $T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

### **TYPICAL PERFORMANCE CURVES(CONT)**

At  $T_A = +25$ °C,  $V_S = \pm 15$ V, unless otherwise noted.

### APPLICATIONS INFORMATION

The OP177 is unity-gain stable, making it easy to use and free from oscillations in the widest range of circuitry. Applications with noisy or high impedance power supply lines may require decoupling capacitors close to the device pins. In most cases  $0.1\mu\text{F}$  ceramic capacitors are adequate.

The OP177 has very low offset voltage and drift. To achieve highest performance, circuit layout and mechanical conditions must be optimized. Offset voltage and drift can be degraded by small thermoelectric potentials at the op amp inputs. Connections of dissimilar metals will generate thermal potential which can mask the ultimate performance of the OP177. These thermal potentials can be made to cancel by assuring that they are equal in both input terminals

- 1. Keep connections made to the two input terminals close together.

- 2. Locate heat sources as far as possible from the critical input circuitry.

- 3. Shield the op amp and input circuitry from air currents such as cooling fans.

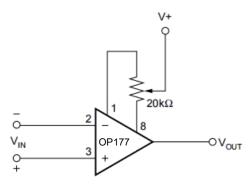

### OFFSET VOLTAGE ADJUSTMENT

The OP177 has been laser-trimmed for low offset voltage and drift so most circuits will not require external adjustment. Figure 1 shows the optional connection of an external potentiometer to adjust offset voltage. This adjustment should not be used to compensate for offsets created elsewhere in a system since this can introduce excessive temperature drift.

### INPUT PROTECTION

The inputs of the OP177 are protected with  $500\Omega$  series input resistors and diode clamps as shown in the simplified circuit diagram. The inputs can withstand  $\pm 30V$  differential inputs without damage. The protection diodes will, of course, conduct current when the inputs are overdriven. This may disturb the slewing behavior of unity-gain follower applications, but will not damage the op amp.

Trim Range is approximately ±3.0mV

### NOISE PERFORMANCE

The noise performance of the OP177 is optimized for circuit impedances in the range of  $2k\Omega$  to  $50k\Omega$ . Total noise in an application is a combination of the op amp's input voltage noise and input bias current noise reacting with circuit impedances. For applications with higher source impedance, the OPA627 FET-input op amp will generally provide lower noise. For very low impedance applications, the OPA27 will provide lower noise.

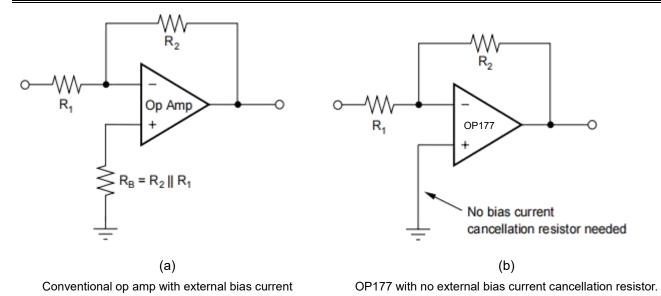

#### INPUT BIAS CURRENT CANCELLATION

The input stage base current of the OP177 is internally compensated with an equal and opposite cancellation current. The resulting input bias current is the difference between the input stage base current and the cancellation current. This residual input bias current can be positive or negative.

When the bias current is cancelled in this manner, the input bias current and input offset current are approximately the same magnitude. As a result, it is not necessary to balance the DC resistance seen at the two input terminals (Figure 2). A resistor added to balance the input resistances may actually increase offset and noise.

cancellation resistor

FIGURE 2. Input Bias Current Cancellation.

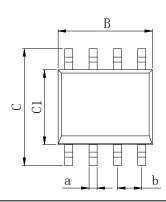

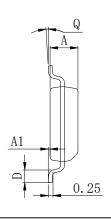

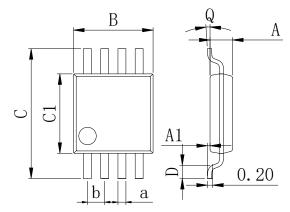

# **PHYSICAL DIMENSIONS**

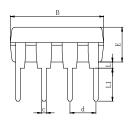

### DIP-8

| Dimensions In Millimeters(DIP-8) |      |      |      |      |      |      |      |      |      |      |          |

|----------------------------------|------|------|------|------|------|------|------|------|------|------|----------|

| Symbol:                          | Α    | В    | D    | D1   | Е    | L    | L1   | а    | b    | С    | d        |

| Min:                             | 6.10 | 9.00 | 8.10 | 7.42 | 3.10 | 0.50 | 3.00 | 1.50 | 0.85 | 0.40 | 0.54.000 |

| Max:                             | 6.68 | 9.50 | 10.9 | 7.82 | 3.55 | 0.70 | 3.60 | 1.55 | 0.90 | 0.50 | 2.54 BSC |

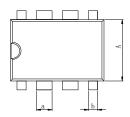

SOP-8

| Dimensions In Millimeters(SOP-8) |      |      |      |      |      |      |    |      |          |  |

|----------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                          | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                             | 1.35 | 0.05 | 4.90 | 5.80 | 3.80 | 0.40 | 0° | 0.35 | 1 27 DCC |  |

| Max:                             | 1.55 | 0.20 | 5.10 | 6.20 | 4.00 | 0.80 | 8° | 0.45 | 1.27 BSC |  |

### MSOP-8

| Dimensions In Millimeters(MSOP-8) |      |      |      |      |      |      |    |      |          |  |

|-----------------------------------|------|------|------|------|------|------|----|------|----------|--|

| Symbol:                           | Α    | A1   | В    | С    | C1   | D    | Q  | а    | b        |  |

| Min:                              | 0.80 | 0.05 | 2.90 | 4.75 | 2.90 | 0.35 | 0° | 0.25 | 0.65 BSC |  |

| Max:                              | 0.90 | 0.20 | 3.10 | 5.05 | 3.10 | 0.75 | 8° | 0.35 | 0.00 BSC |  |

# **REVISION HISTORY**

| DATE      | REVISION                                                                   | PAGE   |  |  |

|-----------|----------------------------------------------------------------------------|--------|--|--|

| 2016-8-7  | New                                                                        | 1-14   |  |  |

| 2022 0 44 | Update encapsulation type、Update Lead Temperature、Updated DIP-8 dimension、 |        |  |  |

| 2023-9-14 | Add annotation for Maximum Ratings.                                        | 1、3、11 |  |  |

#### **IMPORTANT STATEMENT:**

Huaguan Semiconductor reserves the right to change its products and services without notice. Before ordering, the customer shall obtain the latest relevant information and verify whether the information is up to date and complete. Huaguan Semiconductor does not assume any responsibility or obligation for the altered documents.

Customers are responsible for complying with safety standards and taking safety measures when using Huaguan Semiconductor products for system design and machine manufacturing. You will bear all the following responsibilities: Select the appropriate Huaguan Semiconductor products for your application; Design, validate and test your application; Ensure that your application meets the appropriate standards and any other safety, security or other requirements. To avoid the occurrence of potential risks that may lead to personal injury or property loss.

Huaguan Semiconductor products have not been approved for applications in life support, military, aerospace and other fields, and Huaguan Semiconductor will not bear the consequences caused by the application of products in these fields. All problems, responsibilities and losses arising from the user's use beyond the applicable area of the product shall be borne by the user and have nothing to do with Huaguan Semiconductor, and the user shall not claim any compensation liability against Huaguan Semiconductor by the terms of this Agreement.

The technical and reliability data (including data sheets), design resources (including reference designs), application or other design suggestions, network tools, safety information and other resources provided for the performance of semiconductor products produced by Huaguan Semiconductor are not guaranteed to be free from defects and no warranty, express or implied, is made. The use of testing and other quality control technologies is limited to the quality assurance scope of Huaguan Semiconductor. Not all parameters of each device need to be tested.

The documentation of Huaguan Semiconductor authorizes you to use these resources only for developing the application of the product described in this document. You have no right to use any other Huaguan Semiconductor intellectual property rights or any third party intellectual property rights. It is strictly forbidden to make other copies or displays of these resources. You should fully compensate Huaguan Semiconductor and its agents for any claims, damages, costs, losses and debts caused by the use of these resources. Huaguan Semiconductor accepts no liability for any loss or damage caused by infringement.